레이더 및 통신 산업은 실시간으로 다중 신호를 분석·처리해야 하는 복잡한 환경에 직면해 있다. 특히 소출력 레이다 시스템에서는 직교형 신호 송수신을 구현하기 위해 높은 연산 성능과 안정성이 요구된다. 기존 CPU 기반 방식은 성능 한계로 인해 신호 간섭 억제, 정합 필터 뱅크 처리, 파이프라인 구조 수신기 구현에서 효율적 대응이 어려웠다. 이러한 한계는 FPGA(Field-Programmable Gate Array) 기반 실시간 신호처리로 전환을 필수로 만들었다.

테크니컬 컴퓨팅 소프트웨어 전문기업 매스웍스(MathWorks)는 한국전자통신연구원(ETRI)이 직교형 레이다 신호 송수신용 실시간 신호처리 모듈 개발 과정에서 매트랩(MATLAB)과 시뮬링크(Simulink)를 활용했다고 발표했다.

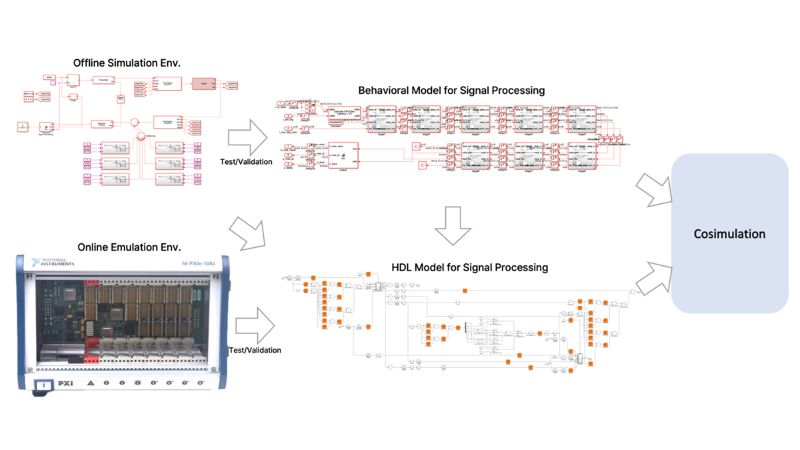

ETRI 전파연구본부는 CPU 기반의 한계를 극복하고 성능 목표를 달성하기 위해 NI FPGA 전환을 선택했으나, 기존 수동 HDL 코드 작성은 비효율성과 오류 발생 위험이 컸다. 알고리듬 변경 시 반복 코딩이 필요했고, 구조 불일치로 인한 디버깅 난이도도 문제였다. 이를 해결하기 위해 연구팀은 알고리듬을 시뮬링크 모델로 변환하고, HDL 코더(HDL Coder)를 통해 자동으로 HDL 코드를 생성하는 워크플로우를 도입했다.

HDL 자동 코드 생성 방식은 FPGA 설계 옵션을 쉽게 검토할 수 있도록 지원했다. 아키텍처, 고정소수점 데이터 타입, 구현 방법을 효과적으로 평가할 수 있었고, HDL 베리파이어(HDL Verifier)를 통해 원본 알고리듬과 HDL 코드의 동작을 코시뮬레이션으로 검증했다.

김형중 ETRI 책임연구원은 “매트랩 펑션 블록을 활용하면 주요 알고리듬 코드를 별도 수정 없이 적용할 수 있어 특히 유용했다”며, “HDL 전문 지식이 없어도 HDL 코더를 활용해 손쉽게 HDL 코드 변환이 가능했다”고 말했다. 이로써 연구팀은 기존 대비 코드 구현·검증 시간과 노력을 50% 절감했다. 또한 알고리듬 설계자와 하드웨어 엔지니어 간 워크플로우 통합으로 반복 작업과 인적 오류를 크게 줄였다.

매스웍스코리아 정승혁 애플리케이션 엔지니어는 “이번 사례는 모델 기반 설계 접근법이 한국의 첨단 연구개발 프로젝트에서 혁신을 가능하게 한 대표적 성과”라며, “앞으로도 선도 연구기관과 협력해 차세대 기술 개발을 지원할 것”이라고 밝혔다. ETRI는 머신러닝 기반 알고리듬을 포함한 차세대 프로젝트에서도 동일한 워크플로우를 적용해 자동 코드 생성을 적극 확대할 계획이다.

관련기사

- 매스웍스-에버소스 에너지, 재생에너지 통합 시스템 개발...전력망 불확실성 해소

- 매스웍스코리아, 매트랩 AI 경진대회 개최

- 예측가능한 배터리 관리 'AI BMS 시장'...EV와 동반 성장

- ETRI, ‘차세대 휴머노이드 브레인’ 개발 본격 착수

- ETRI, 산·학·연 AI 네트워크 기술 협력 ‘ONK 2025’ 개최

- ETRI, AI안전컨소시엄 본격 가동...국가AI 거버넌스 중심 역할 강화

- ETRI-LG AI연구원, AI 학습데이터 신뢰성·안전성 강화 협력

- 매스웍스, 생성AI 기반 ‘매트랩 코파일럿’ 공개...엔지니어링 개발 속도·정확성↑

- AI 제습 제어로 오차 ‘0’ 실현...국내 연구진, 초미세먼지 실시간 측정기 개발

- ETRI, AI·로봇·바이오 오픈소스 R&D 성과 공개

- 보행자 진입 3초 전 위험 예측·알림...사고 예방 효과 검증

- 매스웍스코리아, 제5회 매트랩 대학생 AI 경진대회 시상식 개최