최근 대형언어모델(LLM) 및 생성AI의 개발이 AI 기반 애플리케이션 배포가 가속되고 있어, 더 규모가 크고 효율적인 머신러닝(ML) 모델들이 AI 가속 워크로드에 중요한 역할을 하고 있다. 이처럼. AI를 위한 컴퓨팅 플랫폼 확장은 I/O 대역폭을 기하급수적으로 증가시키고 있다.

xPU 분리(disaggregation) 및 메모리 풀링(memory pooling)과 같은 보다 효율적인 리소스 활용으로 더 큰 처리 장치(CPU/GPU/IPU) 클러스터 및 아키텍처의 지원을 위해 긴거리 통신이 필요하다. 전기 I/O(예: 구리 트레이스 연결)는 고대역폭 집적도와 저전력을 지원하지만 약 1미터 이하의 짧은 거리까지만 제공한다. 데이터 센터 및 초기 AI 클러스터에 사용되는 플러그형 광 트랜시버 모듈(Pluggable optical transceiver modules)은 AI 워크로드에 필요한 확장 요건에 따라 거리를 늘릴 수 있으나 비용과 전력이 지속 가능하지 않은 수준이다.

서버 간 데이터 이동이 지속적으로 증가함에 따라 오늘날 데이터센터 인프라의 성능에 부담이 가중되고 있으며, 현재 솔루션은 빠르게 전기 I/O 성능의 실질적인 한계에 가까워지고 있다.

코-패키징 xPU 광학 I/O 솔루션은 AI/ML 인프라 확장에 필수적인 향상된 전력 효율성, 낮은 대기 시간, 더 긴 도달 거리 및 대역폭을 지원할 수 있다. 예를 들면 데이터 전송을 위해 CPU와 GPU에서 전기 I/O를 광학 I/O로 교체하는 것은 용량과 범위가 제한된 상품을 배포하기 위해 마차를 사용하는 것에서 훨씬 더 많은 양의 물건을 더 멀리까지 전달할 수 있는 자동차와 트럭을 사용하는 것으로 바뀌는 것으로 비유할 수 있다. 이러한 수준의 향상된 성능과 에너지 비용을 광학 I/O 솔루션이 AI 확장에 활용될 수 있다.

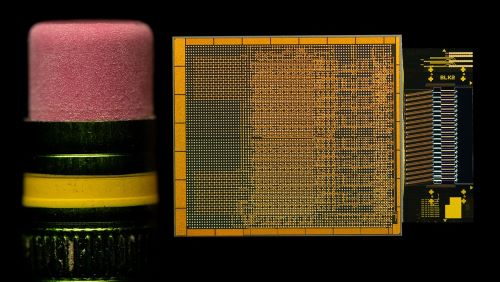

인텔이 미국 샌디에이고에서 개최된 광통신 전시회 ‘OFC 2024(Optical Fiber Communication Conference 2024)’에서 확장 가능한 AI 인프라를 위한 최초의 완전 통합형 광학 입출력(I/O) 칩렛(Chiplet)을 구현했다고 발표했다.

OCI 칩렛, 데이터센터·HPC 애플리케이션용 AI 인프라 고대역폭 인터커넥트 구현

인텔 IPS(Integrated Photonics Solutions) 그룹은 완전 통합 광학 컴퓨트 인터커넥트(Optical Compute Interconnect, 이하 OCI) 칩렛을 인텔 CPU에 코-패키징(co-packaged)하여 실시간 데이터를 실행하는 최첨단 기술을 선보였다. 인텔의 OCI 칩렛은 데이터 센터 및 고성능 컴퓨팅(HPC) 애플리케이션용 AI 인프라에서 코-패키징된 광학 I/O을 지원해 고대역폭 인터커넥트를 구현한다.

OCI 칩렛은 최대 100m의 광섬유에서 각 방향으로 32Gbps 데이터 전송 64채널을 지원해 더 높은 대역폭, 더 낮은 전력 소비, 더 긴 도달 거리에 대한 AI 인프라를 충족시킬 수 있다. 또한, 일관된 메모리 확장 및 리소스 분리를 포함한 새로운 컴퓨팅 아키텍처와 CPU/GPU 클러스터 연결의 향후 확장성을 지원한다.

통합된 OCI 칩렛은 현장에서 입증된 인텔의 실리콘 포토닉스 기술을 활용하고 온칩 레이저 및 광 증폭기를 포함하는 실리콘 포토닉스 집적회로(PIC)를 전기 IC와 통합시킨다. OFC에서 구현된 OCI 칩렛은 인텔 CPU와 함께 패키징 되었지만, 차세대 CPU, GPU, IPU 및 기타 SOCs(시스템온칩)와 통합할 수도 있다.

통합 OCI 칩렛은 최대 4Tbps 양방향 데이터 전송을 지원하며 PCIe(peripheral component interconnect express) 5세대와 호환된다. 현재 칩렛은 각각 8개의 고집적도 파장 분할 다중화(DWDM) 파장을 전달하는 8개의 광섬유 쌍을 활용하여 최대 100m(실제 적용은 전파 시간 지연으로 인해 수십 미터로 제한될 수 있음)까지 각 방향으로 32Gbps 데이터의 64개 채널을 지원한다.

또한, 코패키징 솔루션은 에너지 효율이 뛰어나며, 플러그형 광 트랜시버 모듈의 약 비트당 15 피코줄(pJ)에 비해 비트당 5 피코줄(pJ)만 소비한다. 이러한 초고효율은 데이터센터와 고성능 컴퓨팅 환경에 중요하며, AI의 지속 불가능한 전력 요구 사항을 해결할 수 있다.

인텔의 차별화 요소는 하이브리드 레이저 온 웨이퍼(laser-on-wafer) 기술을 사용한 탁월한 통합과 직접 통합을 통해 신뢰성을 높이고 비용을 절감할 수 있다는 점이다. 이를 통해 효율성과 성능을 향상시킬 수 있다. 인텔의 대용량 플랫폼은 3200만 개 이상의 통합 온칩 레이저가 탑재된 800만 개 이상의 PIC를 제공하며, 0.1 미만의 레이저 FIT(failures-in-time, 오류율을 나타내는 널리 사용되는 신뢰성 척도)를 갖는다.

이러한 PIC는 플러그형 트랜시버 모듈로 패키징되어 주요 하이퍼스케일 클라우드 서비스 제공업체의 대규모 데이터센터 네트워크에 배치되어 초당 100, 200 및 400 Gbps 애플리케이션에 사용되고 있다. 새롭게 부상하는 800Gbps 및 1.6Tbps 애플리케이션을 지원하기 위한 차세대 200G/lane PIC가 개발 중이다.

현재 OCI 칩렛은 프로토타입이다. 인텔은 일부 고객과 협력하여 OCI를 시스템온칩(SOC)과 함께 광학 I/O 솔루션으로 코-패키징하고 있다.

토마스 릴제버그(Thomas Liljeberg) 인텔 IPS 그룹 제품 관리 및 전략 담당 선임 디렉터는 "고객들은 코-패키징 실리콘 포토닉스 인터커넥트 솔루션을 차세대 컴퓨팅 시스템에 원활하게 통합할 수 있게 되었다. 인텔의 OCI 칩렛은 대역폭을 높이고, 전력 소비를 줄이며, 도달 거리를 늘려 고성능 AI 인프라의 혁신을 약속하는 머신러닝(ML) 워크로드 가속화를 지원한다."라고 말했다.

관련기사

- 인간 두뇌 모방한 ‘뉴로모픽 컴퓨팅’ 눈부신 성장세

- 데이터 수집하는 ‘데이터 브로커’ 멈춤 없는 성장

- 멈춤없는 성장 "자율주행차 시장" 연평균 58% 놀라운 성장세

- 포스트 양자 암호화 기반 네트워크 라우터 'IEG'

- 인텔 3 기술 기반 최첨단 파운드리 노드, AI·슈퍼컴퓨팅 가속화 지원

- 테크노트리-HCL테크, '고급 5G 주도 생성 AI 솔루션' 글로벌 통신 시장 확대 협력

- AI·ML 장점 통합한 ‘복합 AI’ 승승장구

- 데이터브릭스, 데이터·AI 활용 극대화하는 ‘유니티 카탈로그’ 오픈소스로 제공

- "프리시전 AI와 글로벌 인텔리전스 더해 글로벌과 한국서 1위 보안 플랫폼 되겠다"

- 케이투스, '인텔 제온6 프로세서 기반 서버' 출시...AI 성능 및 에너지 효율 향상

- 마베니어-비아비-케이블랩스, 오픈랜 3GPP 보안 보증 테스트 완료

- 극한 상황 견디는 소형화·견고화 커넥터, 다양한 산업에 확산

- AI 데이터센터 에너지 문제, 빅 테크가 해결할 수 있을까?

- 인텔, 내년 18A 기반 클라이언트 및 서버용 프로세서 생산 예고